本文将初步介绍verilog的vscode开发环境准备;后续开发测试皆以这个环境为主,数字电路相比高频电路的难点在于不断堆叠基础单元带来的复杂性,所以单元测试就非常重要.另外要说明的是此后数字电路部分的笔记,是我从最基础的硬件设计语言,到CPU的RTL设计,再到SoC的完整制版的一个记录过程,最初的设想的是做一个可以运行的软核的CPU,但没有想到的是扩展的内容越来越多.

1. 环境部署

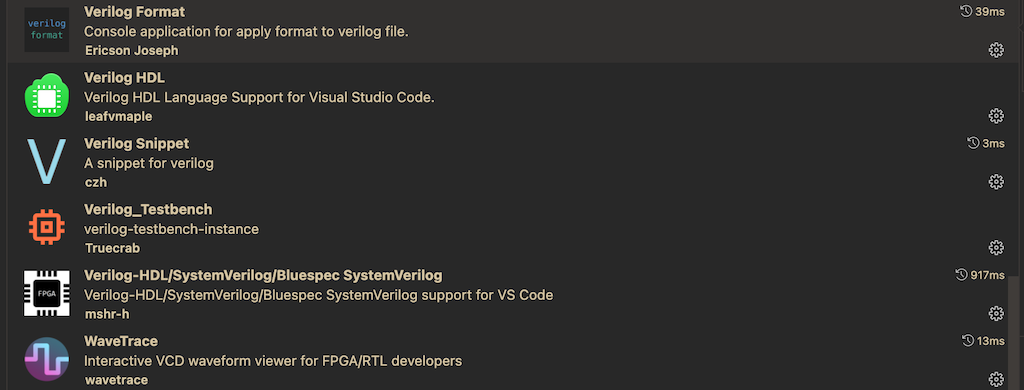

环境部署的内容可以参考这篇文章;熟悉verilog语法,我的建议是下载[VerilogHDL数字设计与综合]这本书精读,从电路本身实现转变到用verilog实现,会在硬件电路设计上走的更远;这里再次附带verilog的安装链接主页;另外确认自己vscode的相关插件都已安装好!!!

2. 工程界面

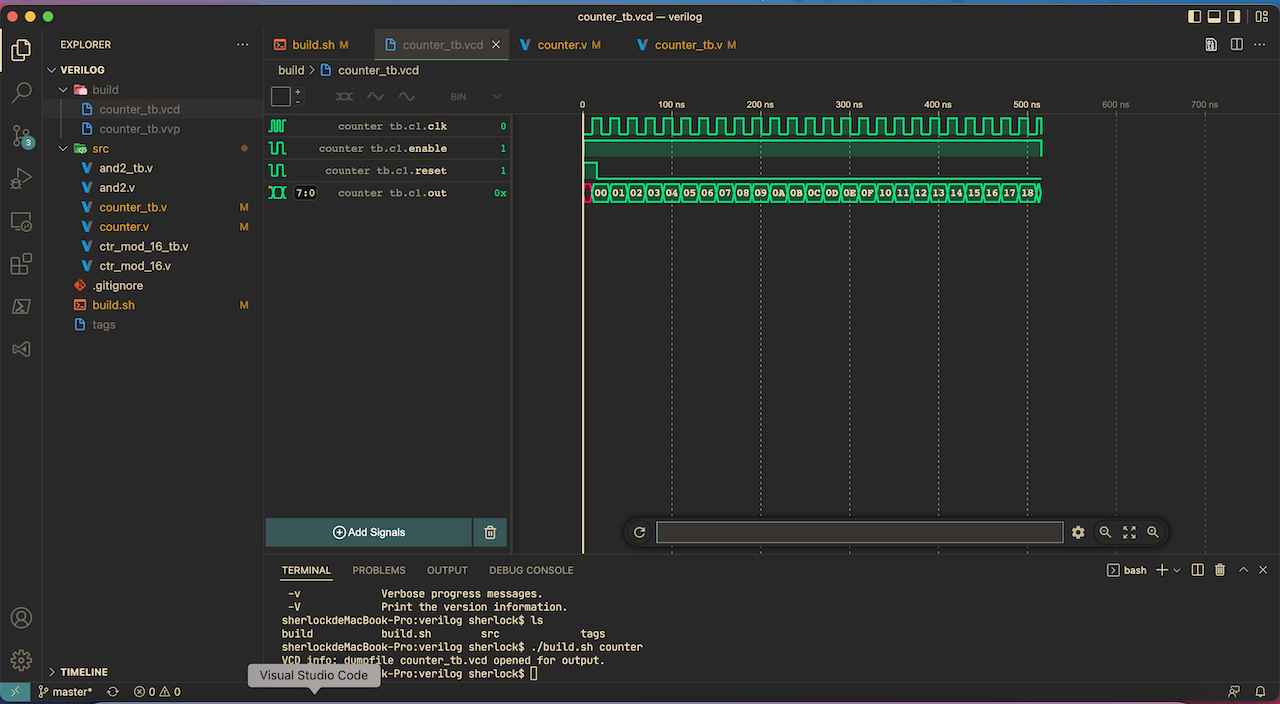

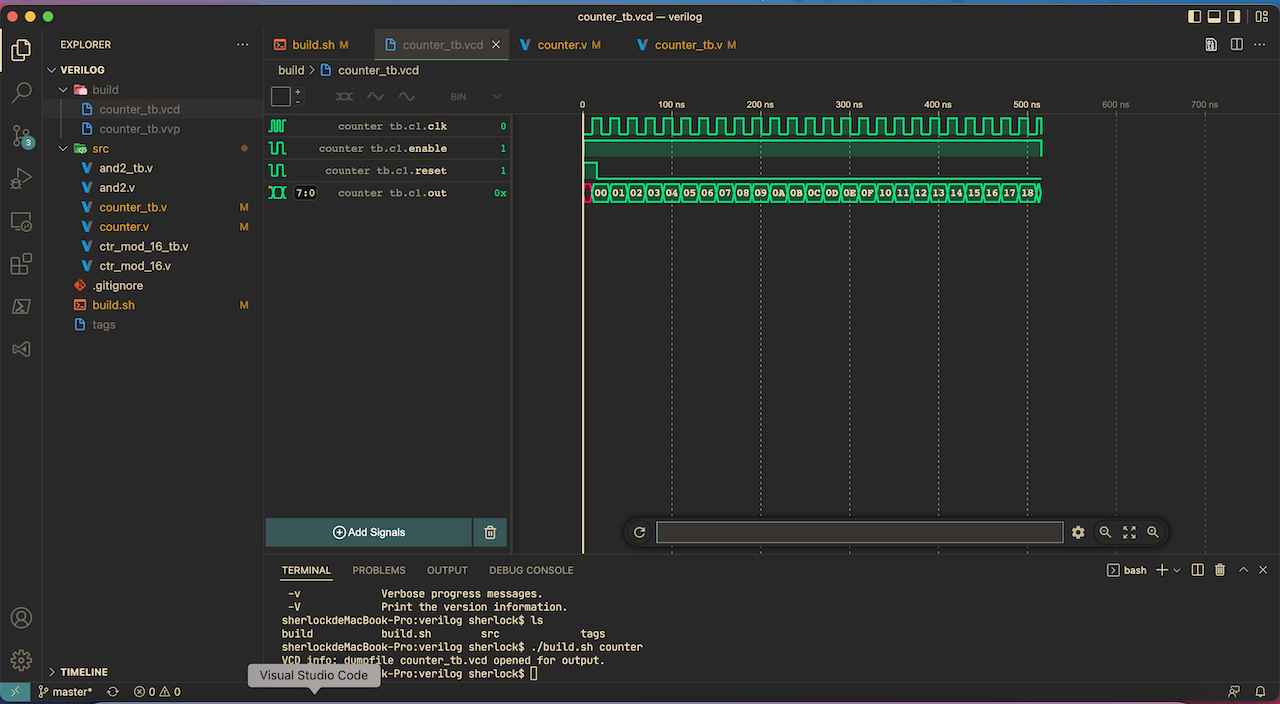

工程目录包括build,src和根目录下的build.sh脚本,src主要是放源码,build存放生成的文件.

3. 工程举例

3.1 编译脚本

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

| #!/bin/bash

work=$(pwd)

build=${work}/build

src=${work}/src

rm -rf ${build}

mkdir -p ${build}

source_module=$1

testbentch_module=${source_module}_tb

cd ${build}

iverilog -o "${testbentch_module}.vvp" ${src}/${testbentch_module}.v \

${src}/${source_module}.v

vvp -n "${testbentch_module}.vvp"

cd ${work}

|

3.2 计数器代码注释

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

|

module counter(out, clk, enable,reset);

output[7:0] out;

input clk, reset, enable;

reg[7:0] out;

always @ (posedge clk) begin

if(reset) begin

out <= 8'b0;

end else if(enable) begin

out <= out + 1;

end

end

endmodule

|

3.3 测试用例注释

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

| `timescale 1ns/1ns

module counter_tb;

reg clk, enable, reset;

wire [7:0] out;

counter c1(.out(out), .clk(clk), .enable(enable), .reset(reset));

initial begin

enable = 1;

end

initial begin

clk = 0;

forever #10 clk = ~clk;

end

initial begin

reset = 1;

#15 reset = 0;

#500 $finish;

end

initial

begin

$dumpfile("counter_tb.vcd");

$dumpvars(0, counter_tb);

end

endmodule

|

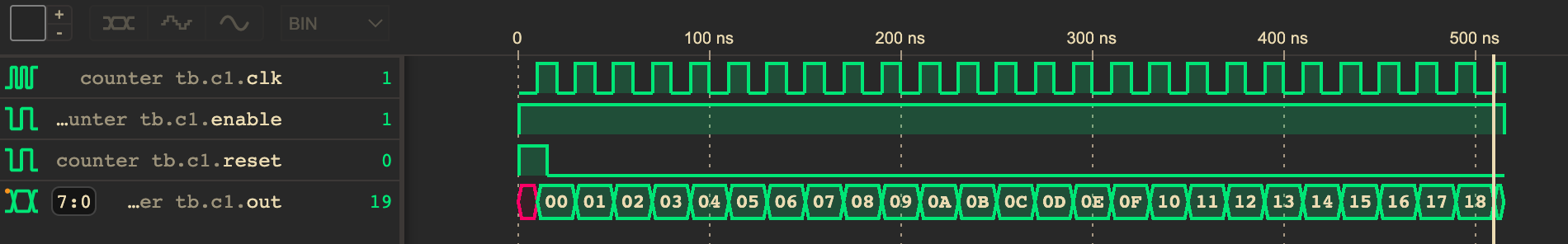

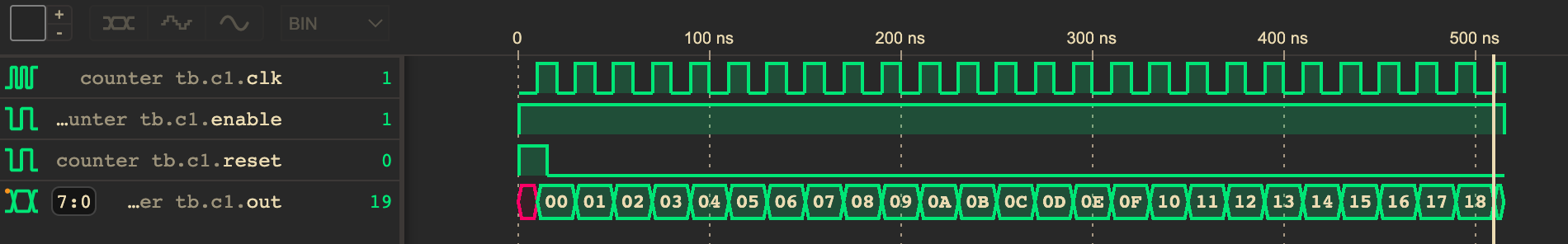

3.4 波形分析

对应3.3测试用例代码解释:

- 第一行是时钟波形,每10ns翻转一次

- 第二行为许可信号,从一开始就为1(高电平)

- 第三行为重置信号,在15ns后为0(低电平)

- 第四行为结果输出,在时钟上升沿时,计数器值增加1

直到第500ns秒结束.